## Portierung des CELT Audiocodecs auf einen ultra low power DSP

Von der Firma Sonova AG erhielt das Embedded Software Engineering Lab den Auftrag, den Audio Codec CELT von einer Referenz-Implementation auf einen spezifischen DSP zu portieren.

### Anwendung

In die Hörgeräte von Sonova soll der neue Bluetooth 5 Standard integriert werden. Das würde in der Zukunft zum Beispiel einen direkten Audio-Stream von einem Smartphone zum Hörgerät über Bluetooth ermöglichen.

### CELT

Constrained-Energy Lapped Transform (CELT) ist ein (patent)-freies Datenformat/Verfahren zur verlustbehafteten Audiodatenkompression mit besonders niedriger Codec-Latenz, um bei Echtzeit-Anwendungen in der Verarbeitung des typischerweise unmittelbar vor der komprimierten Übertragung erzeugten Signales möglichst wenig Verzögerung (Latenzzeit) zu verursachen.

### Cool lux DSP

Als ultra low power DSP wird der CoolFlux DSP von NXP eingesetzt:

- 25  $\mu$ W / MHz

- 24-bit Datenbus

- X und Y Memory

- Dual MAC-Unit

- Ringbuffer Hardwarebeschleunigung

### Ziel

Der portierte Codec soll so wenig Ressourcen wie möglich benötigen. Besonders die RAM und Rechenzyklen sollen auf ein Minimum reduziert werden.

### Resultat

Zu Beginn benötigte der Codec folgende Ressourcen:

- 60 kB RAM

- 35 MHz

Der für den CoolFlux optimierte Codec kommt mit folgenden Ressourcen aus:

- 22 kB RAM

- unter 10 MHz

Die Angaben in MHz ergeben sich aus den zeitlichen Vorgaben der Anwendung.

### Optimierung

Ein Grossteil der RAM-Optimierung konnte dank der Auswahl des effizientesten Datentyps erreicht werden.

Die Reduktion der benötigten Rechenzyklen wurde durch gezieltes Umschreiben von C Code erreicht, ohne die Funktionalität des

Programms zu ändern. Dabei wurde darauf geachtet, dass der erzeugte Assemblercode die Intrinsics der spezialisierten DSP-Architektur für die aufwändigen Algorithmen wie zum Beispiel FFT verwendet.

### Packet Loss Concealment

Für das Packet Loss Concealment (PLC) wird vom Celt Standard kein Algorithmus vorgeschrieben. In der Referenz-Implementation ist jedoch ein Vorschlag vorhanden. Nach einer theoretischen Betrachtung wird dieser PLC um die 40 MHz an Rechenzyklen für den verwendeten DSP brauchen.

Nach der Paper-Suche von gängigen PLC-Algorithmen und der anschliessenden Evaluierung wurde ein geeigneter Algorithmus gefunden, der im Vergleich mit dem Referenz-PLC einen Bruchteil an Ressourcen verbraucht und nur wenig an Qualität einbüsst.

Das Ziel war ein PLC der gleich oder weniger Rechenleistung als der Decoder braucht und somit unter 8 MHz zu liegen kommt. Zusätzlich soll der PLC so wenig zusätzliches RAM wie möglich brauchen.

Der resultierende PLC benötigt knapp 5 MHz Rechenleistung und zusätzliche 2 kB RAM. Eine hörbare qualitative Differenz zum Referenz PLC ist kaum wahrnehmbar.

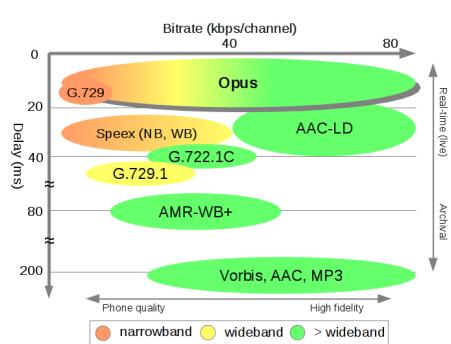

Abbildung 1: Code Qualität in Relation zur Bitrate

(Quelle: Wikipedia)

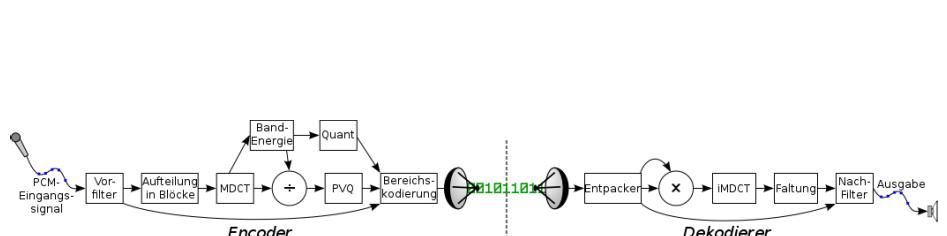

Abbildung 2: Blockdiagramm des Codecs (Quelle: Wikipedia)