## **TeachOS**

## Design and Implementation of an OS for Use in the Operating Systems Lecture Track

Graduate

Fabian Imhof

Matteo Gmür

Introduction: TeachOS is an operating System for the x86\_64 CPU architecture. It is designed to be an interactive learning tool used in the «Operating Systems 1» and «Operating Systems 2» lecture track at OST.

As part of a previous thesis, a foundation in form of memory management, including physical and heap memory was created. Topics covered included parsing Multiboot2 information, implementing frame allocation and page tables, and using these components to remap the kernel. Based on this, dynamic memory allocation during kernel runtime was implemented using different allocation strategies.

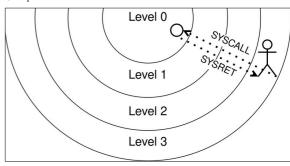

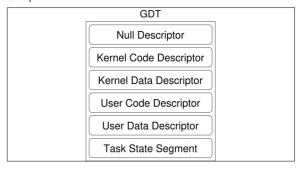

Definition of Task: This paper examines the core concept of context-switching in operating systems for the x86 processor architecture. To implement the context-switch mechanisms, multiple operating system concepts had to be researched and implemented. These concepts include Privilege Levels, the Global Descriptor Table, Interrupts and the Interrupt Descriptor Table and Procedure Calls.

Result: To give the newly created access to user mode a purpose, the existing heap implementation has been expanded upon, by utilizing the new and delete operators in various data-structures. Additionally a separate user mode heap has been created, which is separated from the kernel mode heap via paging, and is dynamically extended when running out of memory.

This foundation can be extended in the future, by separating kernel-code and user-code binaries. Doing this allows for better separation of the different privilege levels inside the paging mechanism, which in turn better resembles real world operating systems, and thus better fulfills the primary goal of providing an operating system designed for education.

**Executing SYSCALL in User Mode**Own presentment

Minimal Global Descriptor Table for Long Mode Setup Own presentment

## **64-bit Segment Descriptor**

Intel 64 and IA-32 Architectures Software Developer's Manual

| 127 |            |    |     |     |     |      |        |      |    |      | 96 |

|-----|------------|----|-----|-----|-----|------|--------|------|----|------|----|

|     |            |    |     |     | F   | Rese | erved  |      |    |      |    |

| 95  |            |    |     |     |     |      |        |      |    |      | 64 |

|     |            |    |     |     |     | Ва   | .se    |      |    |      |    |

| 63  |            |    |     |     |     |      |        |      |    | 32   |    |

| 63  |            | 56 | 55  | 52  | 51  | 48   | 47     | 40   | 39 |      | 32 |

|     | Base       |    | Fla | ags | Liı | mit  | Access | Byte |    | Base |    |

| 31  |            | 24 | 3   | 0   | 19  | 16   | 7      | 0    | 23 |      | 16 |

| 31  |            |    |     |     |     | 16   | 15     |      |    |      | 0  |

|     | Base Limit |    |     |     |     |      |        |      |    |      |    |

| 15  |            |    |     |     |     | 0    | 15     |      |    |      | 0  |

Advisor Felix Morgner

Co-Examiner Hansruedi Patzen, Sonova AG, Stäfa, Zürich

Subject Area Software Engineering